Типы интегральных драйверов MOSFET и IGBT транзисторов

Интегральные драйверы – это специализированные микросхемы для управления MOSFET и IGBT транзисторами. На их входы поступают управляющие сигналы с ШИМ-контроллеров, а их выходные каскады обеспечивают большие импульсные токи (сотни миллиампер - единицы ампер), необходимые для быстрого переключения транзисторов из проводящего состояния в непроводящее и наоборот. То есть фактически они являются усилителями управляющих сигналов по току работающими в импульсном режиме. Это основная функция драйверов. Кроме этого интегральные драйверы могут также совмещать функции инверсии сигнала, обеспечения фазового сдвига, а также функции защиты силового ключа от перегрузки по току. Интегральные драйверы подразделяются в зависимости от топологии преобразователя и расположения ключа, которым они управляют на несколько типов [Современные высоковольтные драйверы MOSFET- и IGBT-транзисторов International Rectifier. Андрей Никитин. Электронные компоненты № 11, 2009. с. 67-71]:

- драйверы нижнего ключа (Low Side Drivers);

- драйверы верхнего ключа (High Side Drivers);

- драйверы полумостовой схемы (Half-Bridge Drivers);

- независимые драйверы верхнего и нижнего ключа совмещённые (High and Low SideDriver).

- изолированные драйверы с оптической развязкой;

- изолированные драйверы с трансформаторной развязкой.

Кроме этого существуют специализированные драйверы однофазного моста и драйверы трёхфазного моста, являющиеся комбинацией двух и трех полумостовых драйверов.

Драйверы нижнего ключа (Low Side Drivers)

Драйверы нижнего ключа используются для управления транзистором относительно уровня «земли». То есть когда исток MOSFET или эмиттер IGBT «сидит» на общей «земле» всей схемы. Это нижние ключи полумостовых и мостовых преобразователей, ключевые элементы обратноходовых (хотя драйверы там особо не нужны), прямоходовых преобразователей, повышающих и инвертирующих импульсных стабилизаторов. Это самые простые по конструкции внутреннего устройства драйверы, имеющие минимальные, по сравнению с другими классами проходные задержки на передачу сигнала от входа к выходу.

Внутренняя структура драйвера нижнего ключа представлена на рисунке GD.1. В общем случае драйвер нижнего ключа содержит: выходной каскад на MOSFET и/или биполярных транзисторах, предусилитель управляющий транзисторами выходного каскада и входной каскад (с возможной функцией гистерезиса по входному напряжению для повышения помехоустойчивости). В качестве примера на рисунке GD.1 представлена внутренняя структура драйверов нижнего ключа серии IR442х и UCC37ххх.

Рисунок GD.1 - Обобщенная внутренняя структура драйвера нижнего ключа и типовая схема управления нижним ключом

Драйверы верхнего ключа (High Side Drivers)

Драйверы верхнего ключа используются для управления транзистором относительно «плавающего» уровня. Как правило, исток MOSFET или эмиттер IGBT «сидит» на выходном «осциллирующем» уровне схемы преобразователя. Это верхние ключи полумостовых и мостовых преобразователей, ключевые элементы понижающих стабилизаторов (типа чоппер), ключи корректоров коэффициента мощности, верхние ключи косых полумостов и т.д.

Драйверы верхнего ключа обязательно содержит в своем составе схему сдвига уровня. Это обусловлено тем, что управляющие импульсы подаются на вход относительно уровня «земли», а выходной каскад драйвера подключен к плавающему уровню. То есть необходимо транслировать управление снизу вверх. Схема сдвига уровня вносит дополнительные задержки и поэтому временные задержки у драйверов верхнего ключа выше, чем у драйверов нижнего ключа. Драйверы верхнего ключа имеют два входа для напряжения питания: одно для питания входного каскада и схемы сдвига уровня, другое для питания выходного каскада.

Внутренняя структура драйвера верхнего ключа представлена на рисунке GD.2:

Рисунок GD.2 - Обобщенная внутренняя структура драйвера верхнего ключа и типовая схема управления верхним ключом

В общем случае драйвер нижнего ключа содержит: выходной каскад на MOSFETтранзисторах, предусилитель управляющий транзисторами выходного каскада, схема сдвига уровня и входной каскад (с возможной функцией гистерезиса по входному напряжению для повышения помехоустойчивости). Кроме этого стандартом «де факто» является блок защиты от пониженного напряжения питания выходного каскада.

Независимые драйверы верхнего и нижнего ключа совмещённые (

High and LowSide Driver)Для управления полумостовыми и мостовыми преобразователями удобно использовать драйверы, совмещающие в одном корпусе драйверы верхнего и нижнего ключей. В общем случае совмещенные драйверы содержат в своем составе драйвер верхнего ключа, драйвер нижнего ключа, схемы сдвига уровня и схемы временной задержки (та самая, которая формирует deadtime) – рисунок GD.3. Кроме этого совмещенные драйверы содержат, как правило, вход стробирования, отключающий оба драйвера. Входы для управления верхним и нижним каналами могут быть как совмещенными в одном, так и раздельными.

Рисунок GD.3 - Обобщенная внутренняя структура совмещенного драйвера верхнего и нижнего ключа и типовая схема управления

Драйверы полумоста (Half-bridge Driver)

Для управления полумостовыми и мостовыми преобразователями удобно использовать специализированные драйверы, совмещающие в одном корпусе драйверы нижнего и верхнего ключей. Драйверы содержат в своем составе драйвер верхнего ключа, драйвер нижнего ключа, схемы сдвига уровня и схемы временной задержки (та самая, которая формирует deadtime) – рисунок GD.4. Кроме этого драйверы содержат, как правило, вход стробирования, отключающий оба драйвера. Входы для управления верхним и нижним каналами могут быть как совмещенными в одном, так и раздельными.

Рисунок GD.4 - Обобщенная внутренняя структура драйвера полумоста и типовая схема включения

Изолированные оптические драйверы силовых ключей

При необходимости полной гальванической развязки при управлении силовым ключом используют специализированные оптические драйверы силовых ключей. Оптодрайвер содержит в своем составе быстродействующий оптрон и собственно драйвер с мощным выходным каскадом. Ключевыми преимуществами является возможность полной гальванической развязки, что важно в случае исток MOSFET (эмиттер IGBT) управляемого транзистора «плавает» в широких пределах. Это обеспечивает некоторую независимость силовой цепи от цепи от цепи управления и повышает ремонтопригодность в случае критических проблем в силовой части. Недостатками являются существенно большие временные задержки, по сравнению с неизолированными драйверами (сотни наносекунд по сравнению с десятками) и необходимость обеспечения питания силовой части драйвера с помощью отдельного гальваноразвязанного маломощного источника напряжения. В качестве последнего могут быть использованы дешевые flyback-преобразователи или низкочастотные трансформаторы с выпрямителем и стабилизатором. Представленные преимущества и недостатки определяют основную область использования оптических драйверов – управление IGBT-транзисторами на небольших частотах – до 20-50 кГц.

При необходимости специальных применений можно использовать совмещение быстродействующей оптопары (предназначенной для использования в волоконных линиях связи) и обычного драйвера нижнего ключа.

Основные параметры интегральных драйверов:

Основные параметры интегральных драйверов представлены в таблице GD.1.

Таблица GD.1 - Основные параметры интегральных драйверов

| № | Обозначение | Наименование | ENG-наименование | Описание |

| 1 | IO+ | Максимальный «вытекающий» ток драйвера | Output high short circuit pulsed current | Ток выходного каскада драйвера во включенном состоянии при условии короткого замыкания на выходе |

| 2 | IO- | Максимальный «втекающий» ток драйвера | Output low short circuit pulsed current | Ток выходного каскада драйвера в включенном состоянии при условии что на выходе драйвера уровень напряжения питания |

| 3 | VS | Максимальное напряжение питания драйвера | Fixed supply voltage | Максимальная величина напряжения питания драйвера |

| 4 | VO | Максимальное выходное напряжение драйвера | Output voltage | Максимальная величина напряжения на выходе драйвера (связана с входным напряжением) |

| 5 | PD | Максимальная рассеиваемая мощность | Package power dissipation | Максимальная мощность, рассеваемая корпусом драйвера |

| 6 | VIH | Пороговое напряжение логической единицы | Logic “1” input voltage | Пороговый уровень входного напряжения выше которого драйвер переходит в состояние «включено» |

| 7 | VIL | Пороговое напряжение логического нуля | Logic “0” input voltage | Пороговый уровень входного напряжения ниже которого драйвер переходит в состояние «выключено». При отсутствии гистерезиса по входу VIH = VIL = VIN_H (logic 1 input threshold) |

| 8 | IIN+ | Входной ток управляющего сигнала в состоянии включено | Logic “1” input bias current (OUT=HI) | Максимальный уровень входного тока входа управления в состоянии «включено» |

| 9 | IIN- | Выходной ток управляющего сигнала в состоянии включено | Logic “0” input bias current (OUT=LO) | Максимальный уровень выходного тока входа управления в состоянии «выключено» |

| 10 | IQS | Ток покоя драйвера | Quiescent Vs supply current | Ток собственного потребления интегрального драйвера |

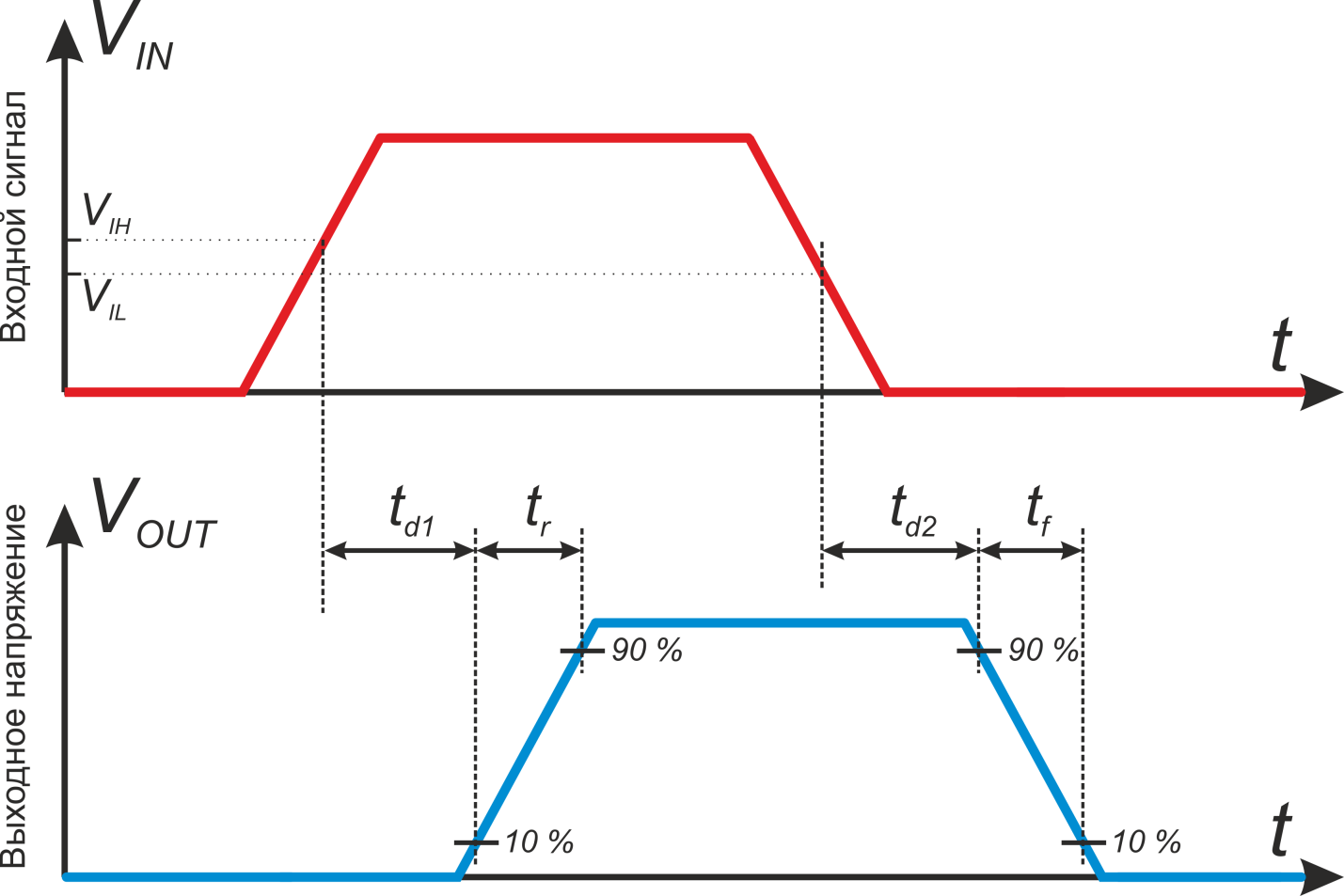

| 11 | td1 | Задержка передачи сигнала включения | Turn-on propagation delay | Время от перехода входным сигналом порогового уровня до начала нарастания (10% или 20% от уровня) напряжения на выходе драйвера |

| 12 | td2 | Задержка передачи сигнала выключения | Turn-off propagation delay | Время от перехода входным сигналом порогового уровня до начала спада (90% или 80% от уровня) напряжения на выходе драйвера |

| 13 | tr | Длительность фронта нарастания импульса | Turn-on rise time | Время нарастания напряжения на выходе драйвера от 10% или 20% до 90 % или 80% от максимума |

| 14 | tf | Длительность фронта спада импульса | Turn-off fall time | Время спада напряжения на выходе драйвера от 90% или 80% до 10 % или 20% от максимума |

Для драйверов верхнего ключа, а также совмещённых и полумостовых драйверов кроме перечисленных существует ряд дополнительных параметров:

Таблица GD.2 Специфические параметры совмещённых и полумостовых драйверов интегральных драйверов

| № | Обозначение | Наименование | ENG-наименование | Описание |

| 1 | VB | Максимальное напряжение смещения питания выходного каскада | High Side Floating Supply Voltage | Максимальное напряжение между уровнем напряжения питания выходного каскада с «плавающим» потенциалом и уровнем «земли» |

| 2 | VS | Максимальное напряжение смещения | High Side Floating Offset Voltage | Максимальное напряжение между нижним уровнем выходного каскада (исток или эмиттер верхнего транзистора), средняя точка полумоста и «землей» |

| 3 | dVs/dt | Максимальная скорость нарастания напряжения на плавающем электроде | Allowable Offset Supply Voltage Transient | Максимальное значение скорости нарастания напряжения на плавающем электроде. При превышении это скорости возможно паразитное открывание драйвера и сквозной ток в силовой части. |

| 4 | VS_neg | Максимальное отрицательное напряжение плавающего потенциала | Maximum VS Negative Offset | Максимальная величина отрицательного напряжения плавающего потенциала относительно уровня «земли». Этот параметр характеризует стойкость микросхемы к защелкиванию, которая возникает при работе на индуктивную нагрузку. Чем больше тем лучше. Обычно указывается в справочных листках в формате графика зависимости от напряжения питания выходного каскада (Maximum VS Negative Offset vs. Supply Voltage). |

Дополнительные функции драйверов

- Дифференциальные входы. Иногда входы драйверов делают дифференциальными с целью увеличения возможностей управления (важно для контроллеров моторов).

- Блокировка при уменьшении напряжения питания ниже порогового уровня (UVLO - Under Voltage Lock-Out threshold). Пониженное напряжение питания выходного каскада может привести к росту динамических потерь или его переходу в активный режим, что вызовет быстрый выход его из строя.

- Защита от короткого замыкания. Суть защиты заключается в непрерывном контроле тока истока MOSFET (или эмиттера у IGBT) либо путем использования низкоиндуктивных шунтов, включающихся в цепь истока (эмиттера), либо путем контроля напряжения на открытом ключе. Драйвер с функцией защиты от короткого замыкания с использованием шунта содержит вход контроля тока и внутренний компаратор, аварийно выключающий ключ при превышении током установленного значения. Если контроль короткого замыкания осуществляется по напряжению на стоке (коллекторе), то драйвер содержит дополнительный вывод, соединяемый как правило через диод со стоком (коллектором) и аналогичную компараторную схему, аварийно выключающую силовой ключ [Драйверы силовых ключей. Георгий Волович. СОВРЕМЕННАЯ ЭЛЕКТРОНИКА. № 8. 2007. с. 32-40].

- Формирование временной задержки. Для предотвращения возможных сквозных токов драйверах полумостовых схем может присутствовать функция формирования временной задержки между каналами управления верхнего и нижнего ключей (рисунок GD.5). Задержка нужна для того чтобы дать одному из ключей выключится прежде чем начнет включаться второй. Длительностью задержки, как правило, можно управлять.

Рисунок GD.5 - Динамические задержки между входными и выходными сигналами интегральных драйверов MOSFET и IGBT транзисторов